6月赛灵思推出了两款易于扩展的、超高密度视频转码专用视频实时转码一体机。基于新型的赛灵思实时服务器( Xilinx RT Server)参考架构,两大全新一体机将双管齐下,助力当今服务提供商以每通道最低成本提供视频质量和比特率优化的多种类型应用。本文我们将为您揭开这一与众不同的实时转码一体机...

视频直播已经成为当前一个关键的业务需求。来自各种各样的远程办公、在线学习和娱乐等并发视频流量指数级增长,视频服务提供商们的业务魔视面临前所未有的挑战,一发明要控制其不断推高的基础架构和运营成本,一方面还要保障为用户提供高品质的直播体验。鉴于视频转换的计算密度越来越大,转码亟需更高性能、灵活应变的硬件加速平台。

为应对此需求,赛灵思推出了赛灵思视频实时服务器一体机参考架构。基于 Alveo™ 加速卡,无需改变现有基础架构,即可以每通道最低成本实现突破性的视频流性能,较之于固定架构解决方案,能显著降低总拥有成本( TCO )。

对实时视频流的需求给视频服务提供商带来了严峻挑战,因为他们必须在管理基础设施和互联网带宽运营成本的同时,还要为客户提供高质量体验。鉴于视频转换的计算强度,转码不断推升对灵活应变硬件加速的需求。

如今,视频服务提供商运用新一代压缩标准和自适应比特率 (ABR) 视频流协议,在保障高质量视频分发的同时对带宽进行管理。然而,两种方法虽都能降低比特率,但却会提高计算的复杂性。有没有一种鱼与熊掌可兼得的方案呢?

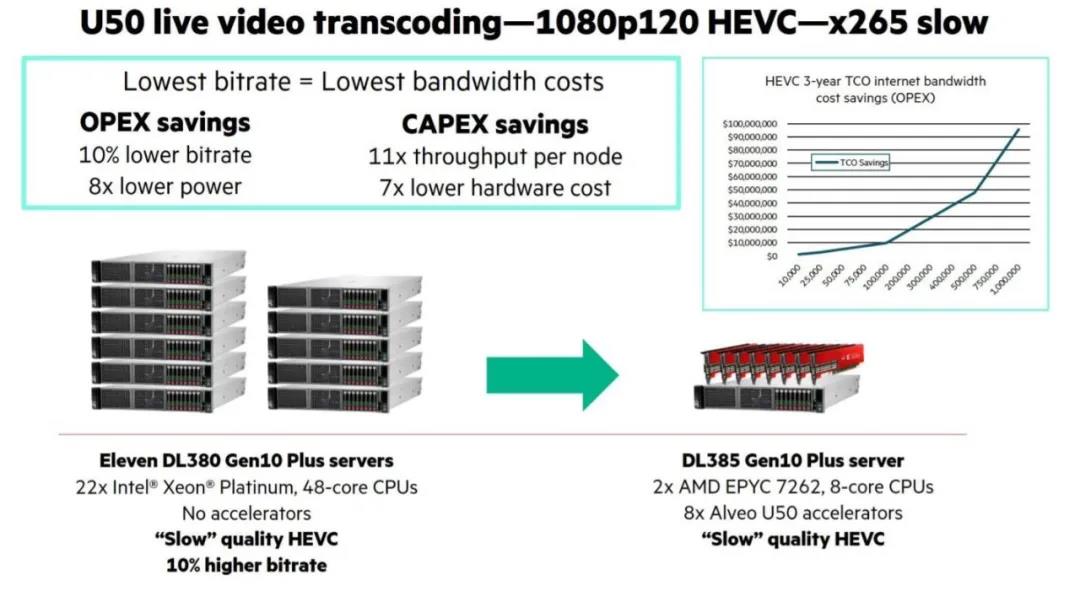

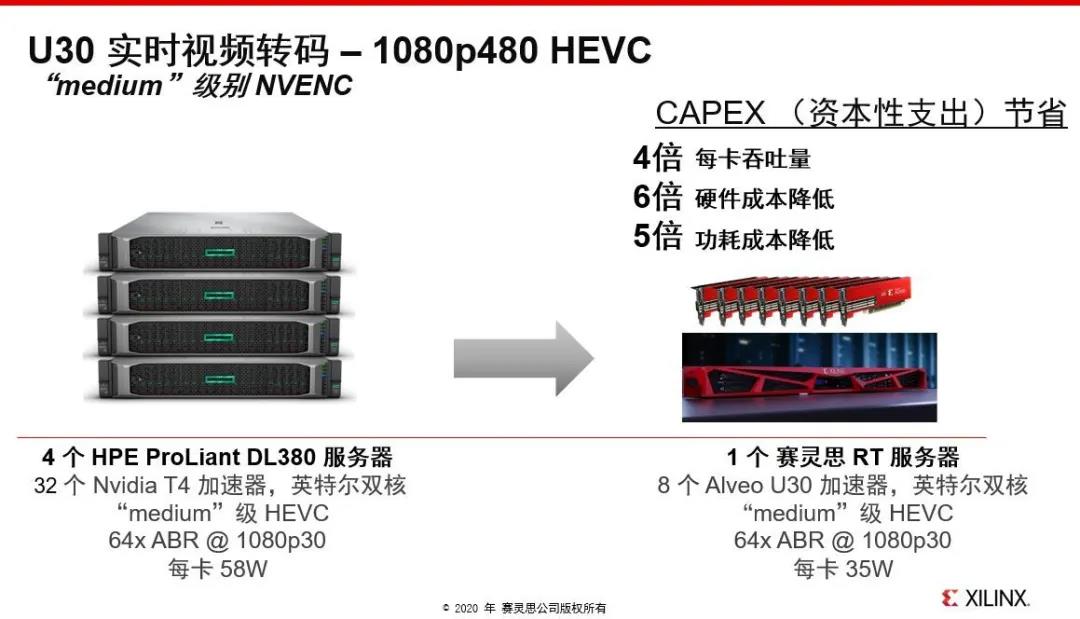

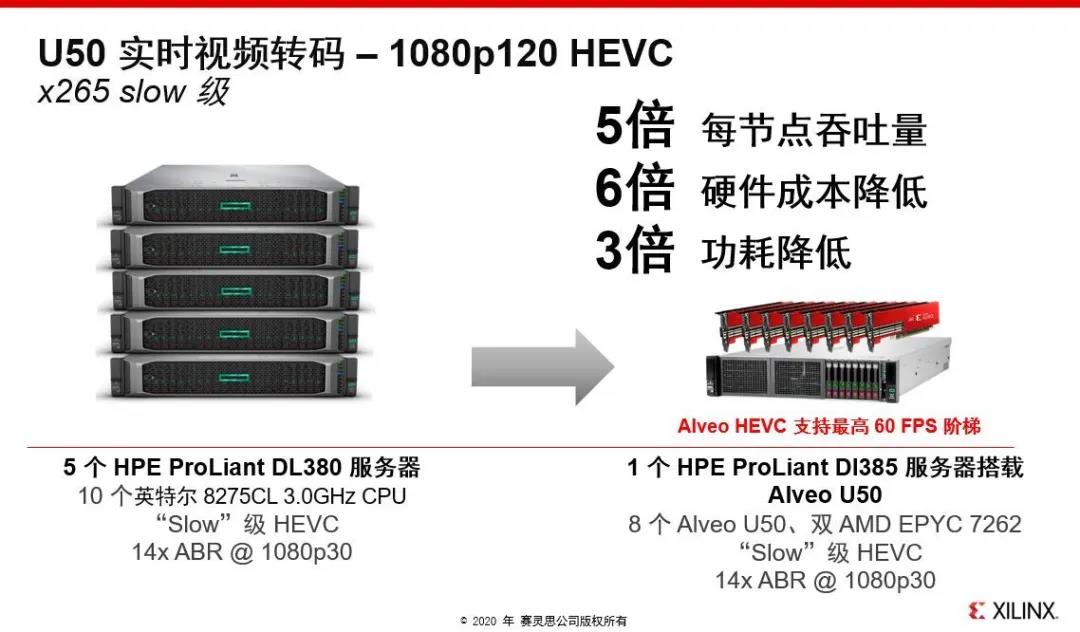

赛灵思与慧与公司 (HPE) 已经开发出一种足以掀起性能革命的最终用户解决方案。该方案使用搭载第二代 AMD EPYC 处理器的 HPE ProLiant DL385 Gen10 Plus 服务器。

图1:HEVC TCO示例

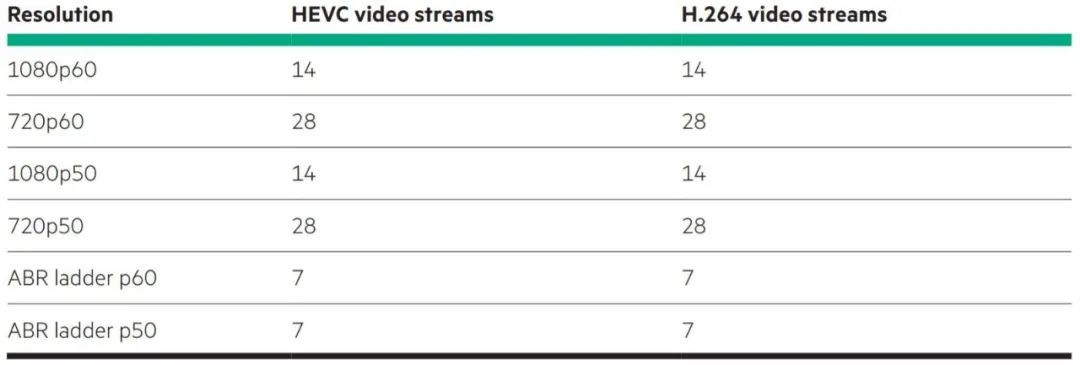

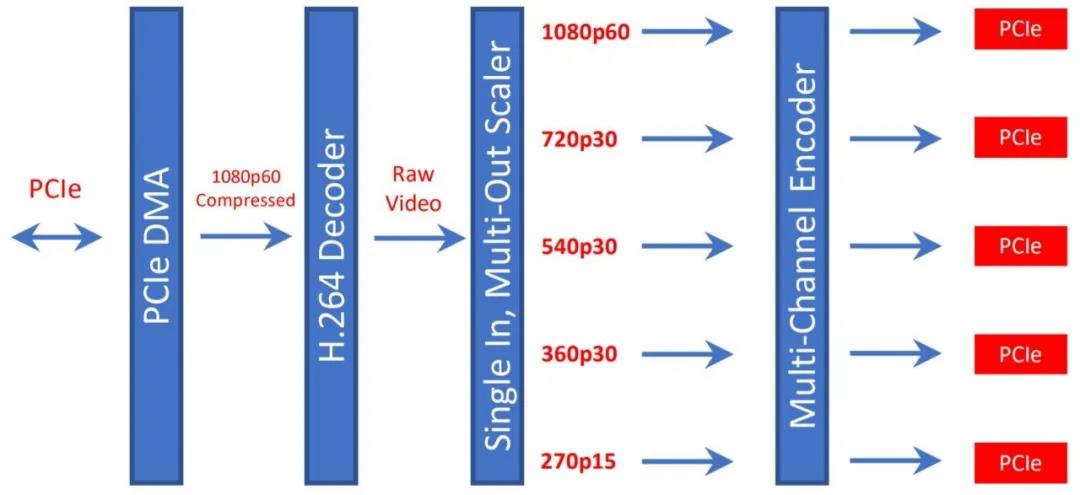

该服务器配置了 7 个 U50 用于编码、1 个 U50 用于 H.264 解码和缩放,能够支持视频流分辨率和全部 ABR 阶梯,如下表所示:

图2:视频流与转码ABR阶梯示例

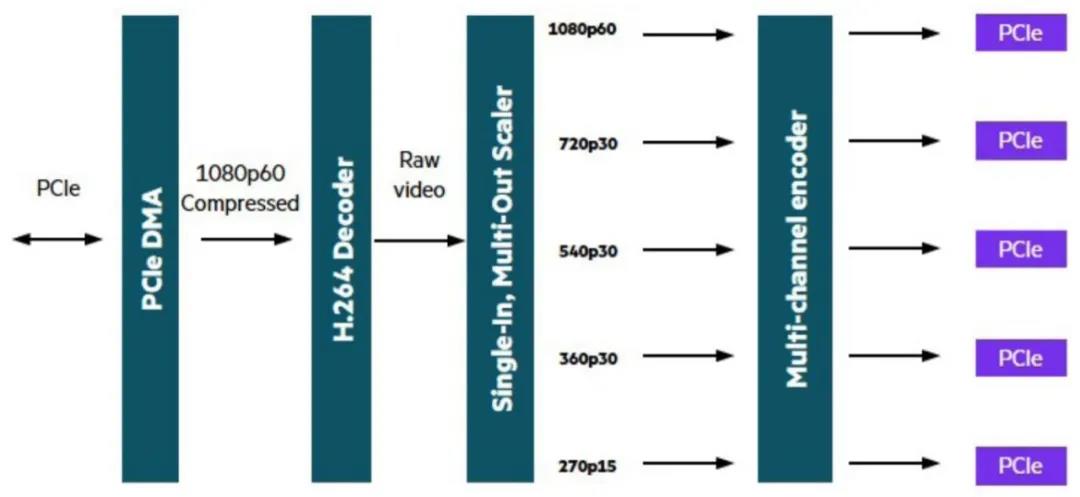

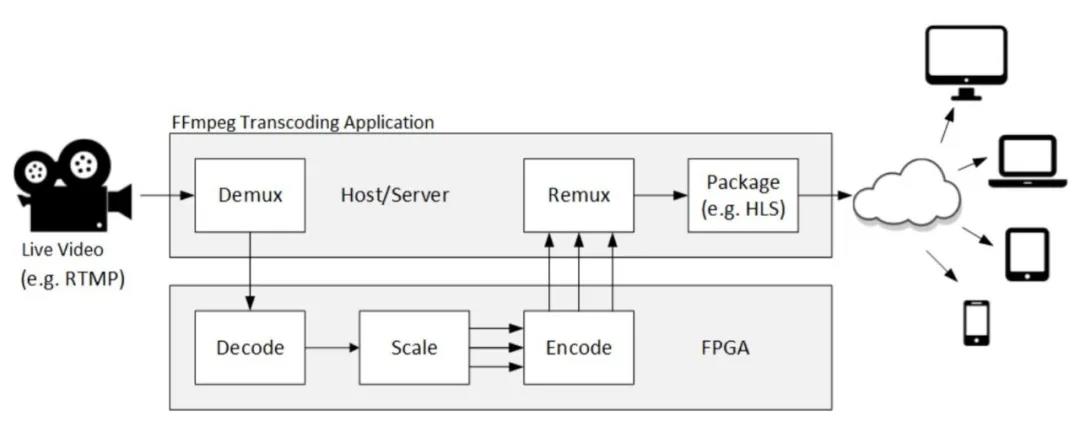

赛灵思与 HPE 携手提供最高系统级性能。通过详细的工作负载配置,能够确保在主机 CPU 和 Alveo 加速器卡之间进行智能功能分区。从 CPU 卸载编码器功能可确保处理器能够为音频处理和广告插入等其他关键任务提供支持。对 FFmpeg 插件的支持有助于客户将 Alveo U50 加速器卡和软件轻松集成到现有基础设施中。标准的命令行窗口也提供了全面控制。

图3:从内容生成器将数据流转到消费端

1080P60 实时编码,具备 x265 慢速画质

提高每节点吞吐量

较低的比特率编码有助于降低网络带宽成本

更低的硬件成本

与基于 CPU 的编码相比功耗更低

用于解码器、定标器和编码器的 FFmpeg 插件

提供软件编码器不具备的确定性性能

HEVC:主 10 配置文件,级别可达 5.1 HD/SD 4:2:0 8 位

H.264:主 10 配置文件,级别可达 5.1 HD/SD 4:2:0 8 位

比特率:从 100Kb/s 到 40Mb/s 可配置

时延:从 100ms 到 10s 可配置

恒定比特率、受限可变比特率 (VBR) 和 ABR 模式

帧类型:I、P 和 B,提供灵活的开放/闭合 GOP 模式和 GOP 长度

低成本 HPE 服务器,提供比软件型解决方案更低的总体拥有成本 (TCO)

CPU 上最低的服务器负载,实现音频处理和广告插入等附加功能

HPE iLO BMC 可支持 Alveo U50 卡

对实时视频流的需求已发展成为一项至关重要的业务需求。视频服务提供商面临着艰难的权衡取舍,因为他们必须在管理基础设施和运营成本的同时,还要为客户提供高质量体验。鉴于视频转换的计算强度,转码不断推升对灵活应变硬件加速的需求。

赛灵思已开发出一款高性能视频转码包,无需改变现有基础设施即可为服务提供商提供所需低功耗与优异性能。

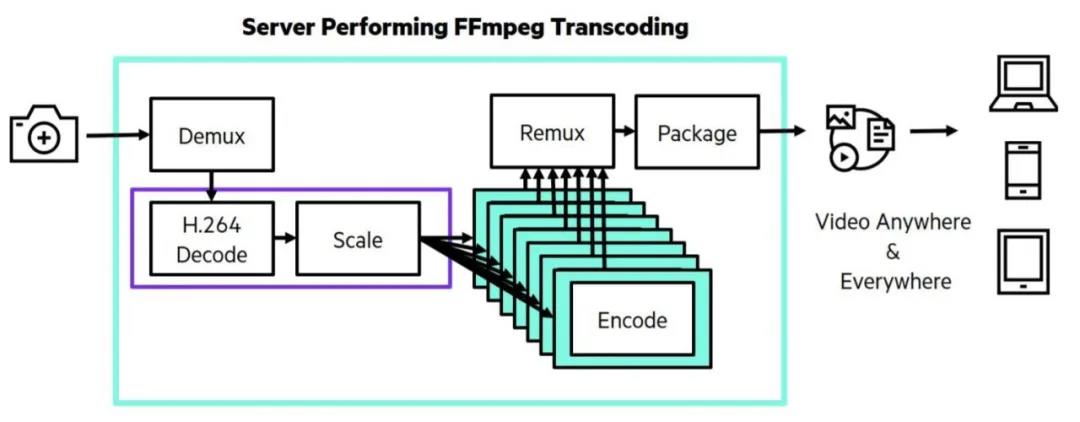

此外,该解决方案采用业经验证的非常强大的 FFmpeg 命令行处理模式,方便任何人开发转码应用并将其与现有应用或自有基础设施轻松集成。

赛灵思面向低比特率(Alveo U50)或高密度应用(Alveo U30)实现最高质量的实时编码,并且以最低的主机 CPU 需求加速编码。另外,在 Alveo U50 和 U30 加速器卡上使用 ABR 阶梯提供 HEVC 和 H.264 编码流以及基于行业标准 FFmpeg 的简单 API。

图4:转码ABR阶梯示例

赛灵思可以提供系统级最高性能。通过从 CPU 卸载编码任务,确保 CPU 能够为音频和广告插入等其他关键功能提供支持。

通过提供对 FFmpeg API 的支持,客户能够轻松地将多达 8 个 Alveo HHHL U50 或 U30 加速器卡和软件集成到其 1 RU 服务器中。

图5:从内容生成器将数据流转码到消费端

实时编码可实现媲美 x265“慢速”预置编码的画质

U50 支持面向海量观众广播的最低水平比特率编码

低比特率 = 最低互联网带宽成本

在需要大量编码器时实现高密度编码,如用户生成内容 (UGC)

与 CPU 相比功耗下降 10 倍

与 GPU 相比功耗下降 2 倍

采用高级定标器,提供完整的 ABR 阶梯支持

灵活的多 ABR 阶梯输出,单个实例最多 32 个流

输出质量保持一致,与编码通道数量无关

用于解码器、定标器和编码器的 FFmpeg 插件

HEVC:主 10 配置文件,级别可达 5.1 HD/SD,U50:4:2:0 8 位,U30:4:2:2 10 位

H.264:主 10 配置文件,级别可达 5.1 HD/SD,U50:4:2:0 8 位,U30:4:2:0 10 位

恒定比特率 (CBR)、受限 VBR 和 ABR 模式

比特率:100Kb/s 到 40Mb/s 可配置

时延:30ms 到 20s 可配置

片类型:I、P 和 B,提供灵活的开放/闭合 GOP 模式和 GOP 长度

赛灵思与全球发展速度最快的硬件学习、编程与构建开发者社区Hackster.io携手推出的首届赛灵思自适应计算挑战赛(Xilinx Adaptive Computing Challenge)。无论你是个人开发者,或是初创企业,你将收获不仅限于一场开发挑战赛!

我们梳理了你将可能获得各样福利:

可以免费申请租用开发板(loaner board)

一系列FPGA相关课程与培训

丰厚奖金:个人开发者最高奖金1万美元,初创企业最高奖金10万美元

全套Xilinx软件开发套件

通过Xilinx官网报名,候选者需要通过审核。详情参阅网站内正式比赛规则。https://china.xilinx.com/community/contest2020.html(注:请使用英文填写申请表)

价格: 1,295 美金

产品编号: EK-U1-ZCU104-G

产品描述:ZCU104 评估套件可帮助设计人员为监控、高级驾驶员辅助系统 (ADAS)、机器视觉、增强实境 (AR)、无人机和医学成像等嵌入式视觉应用快速启动设计。该套件采用带视频编解码器的 Zynq UltraScale+ MPSoC EV 器件,支持嵌入式视觉使用案例的许多常见外设及接口。随附提供的 ZU7EV 器件配备四核 ARM Cortex-A53 应用处理器、双核 Cortex-R5 实时处理器、Mali-400 MP2 图形处理单元、支持 4KP60 的 H.264/H.265 视频编解码器和 16nm FinFET+ 可编程逻辑。

如何获得免费的ZCU104评估套件?

报名Xilinx自适应计算挑战赛,完成申请ZCU104板卡的流程才算报名成功哦~ 项目经Xilinx审核过后即可获得免费的ZCU104评估套件,比赛结束不用归还。 (注,需要在规定时间内提供项目最终方案)